Can't put a Band-Aid on a boomerang Pg 60

R

**Issue 7**/2010

www.edn.com

Lifetime and reliability in LEDs and why SOC designers should care Pg 4

Manager's guide to digital design Pg 15

Design Ideas Pg 45

Supply Chain Pg 56

# COMING SOON:

VOICE OF THE ENGINEER

Page 24

**3-D TV**

COMPLEX MODULATION COMES TO OPTICAL FIBER

Page 32

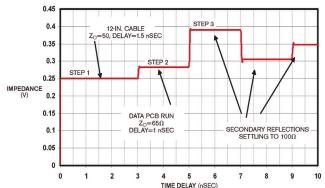

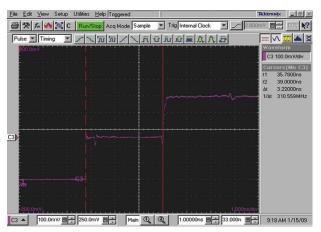

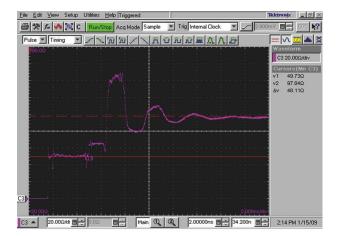

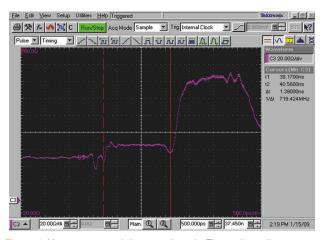

MEASURE PROPAGATION DELAYS USING TIME-DOMAIN REFLECTOMETRY

Page 36

CONTINUOUS-TIME EQUALIZERS IMPROVE HIGH-SPEED SERIAL LINKS Page 40

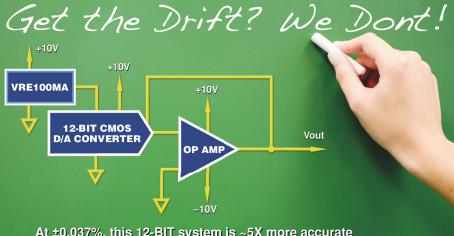

VRE100 SERIES DIP14 PACKAGE

> **NORTH AMERICA** +1 800-625-4084

> **ASIA PACIFIC** +852 2376-0801

**JAPAN** +81 (3) 5226-7757

**EUROPE/UK** +44 (0) 1628-891-300

At ±0.037%, this 12-BIT system is ~5X more accurate than a 16-BIT system over a –55°C to +125°C range

# Cirrus Logic Voltage References Deliver Low Temperature Drift for Better Accuracy

#### LOW INITIAL OFFSET PEFORMANCE ALSO MINIMIZES IMPACT OF OPERATING CONDITIONS

S 41

ie 4

When your system demands voltage supply accuracy, rely on Cirrus Logic to deliver. The VRE series of precision voltage references offer best in class performance for low temperature drift by minimizing the impact of operating conditions on voltage delivery over time. Performance "at temperature" is enhanced further with low initial offsets, improved temperature coefficients and reduced thermal hysteresis. With the quality and reliability of more than 25 models of off-the-shelf solutions, Cirrus Logic can eliminate design cycle headaches and speed time to market.

| Model Specifications |               |                    |                     |  |  |  |

|----------------------|---------------|--------------------|---------------------|--|--|--|

| Series               | Output (V)    | TempCo<br>(ppm/°C) | Feature             |  |  |  |

| VRE302               | 2.5           | 0.6, 1.0, 2.0      | Low Cost            |  |  |  |

| VRE3025              | 2.5           | 0.6, 1.0, 2.0      | +10V Supply         |  |  |  |

| VRE4125              | 2.5           | 1.0, 3.0           | Low Cost, 5V Supply |  |  |  |

| VRE117               | +3            | 0.3, 0.6           | Low Output V        |  |  |  |

| VRE205               | 5             | 0.4, 0.8           | Small Pkg           |  |  |  |

| VRE305               | 5             | 0.6, 1.0, 2.0      | Low Cost            |  |  |  |

| VRE306               | 6             | 0.6, 1.0, 2.0      | Low Cost            |  |  |  |

| VRE100               | +10, -10, ±10 | 0.3, 0.5           | High Rel            |  |  |  |

| VRE210               | 10            | 0.3, 0.5           | Small Pkg           |  |  |  |

| VRE310               | 10            | 0.6, 1.0, 2.0      | Low Cost            |  |  |  |

CIRRUS LOGIC®

TO LEARN MORE ABOUT CIRRUS LOGIC VOLTAGE REFERENCES,OR TO RECEIVE A FREE COPY OF THE LATEST VRE PRODUCT GUIDE, VISIT www.cirrus.com/ednvre

# LEARN MORE AT

For product selection assistance or technical support with Apex Precision Power products call 1-800-546-2739 or apex.support@cirrus.com.

© 2010 Cirrus Logic, Inc. All rights reserved. Cirrus Logic, Cirrus, the Cirrus Logic logo designs, Apex Precision Power, Apex and the Apex Precision Power logo designs are trademarks of Cirrus Logic, Inc. All other brands and product names may be trademarks or service marks of their respective owners. EDN04082010

450,000+ PRODUCTS IN STOCK. 440+ SUPPLIER PARTNERS. 45,000+ NEW PRODUCTS ADDED IN THE LAST 90 DAYS. The industry's broadest product selection available for immediate delivery

### www.digikey.com 1.800.344.4539

Digi-Key is an authorized distributor for all supplier partners. New products added daily. © 2010 Digi-Key Corporation, 701 Brooks Ave. South, Thief River Falls, MN 56701, USA

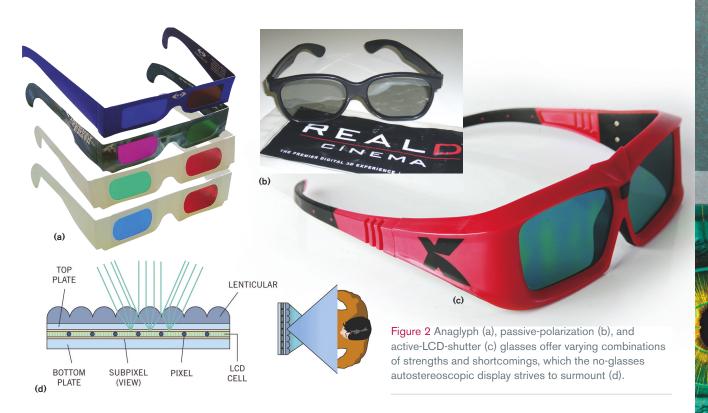

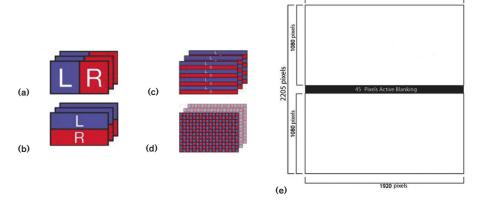

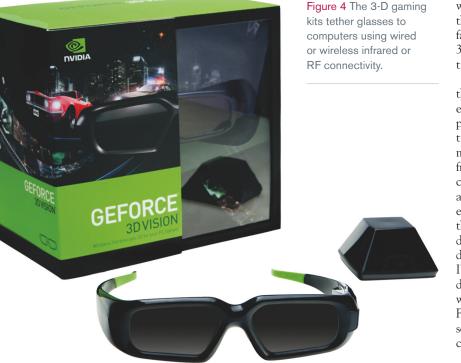

#### Coming soon: 3-D TV

The fact that 3-D is a hot ticket in tech may not surprise you. The fact that it's headed soon to consumers' homes, however, may surprise—and dismay—cinema owners. by Brian Dipert, Senior Technical Editor

# EDN 4.8.10 contents

### LTE in focus

1 7 As LTE networks roll out this year, engineers will be applying various test scenarios in lab and smallscale field tests to the LTE devices and equipment they are developing.

by Reiner Goetz, Anne Stephan, and Meik Kottkamp, Rohde & Schwarz

- 7 Expandable 3.6-, 6-, and 13.5-GHz signal analyzers feature optional built-in generator

- 8 Vitesse zeros in on carrier-Ethernet switch needs

- 9 Single-key capacitive touch controllers target use in portable products

- 9 3-D holographic images deliver er impressive realism, need no glasses

- 10 GaN power transistors take aim at MOSFETs

- 11 Smart FET driver emulates rectifier in secondary-side applications

- 11 Sharp expands its repertoire of LCDs for in-car use

- 12 Rethinking static-timing analysis

- 12 Intel unveils 32-nm datacenter microprocessors

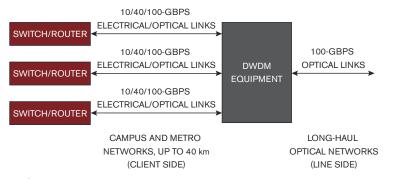

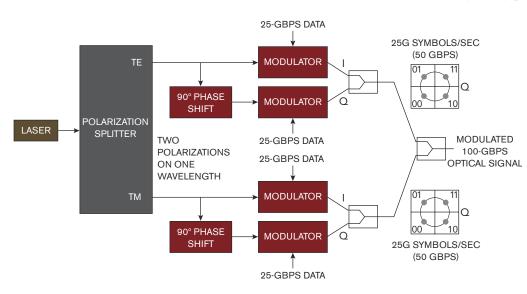

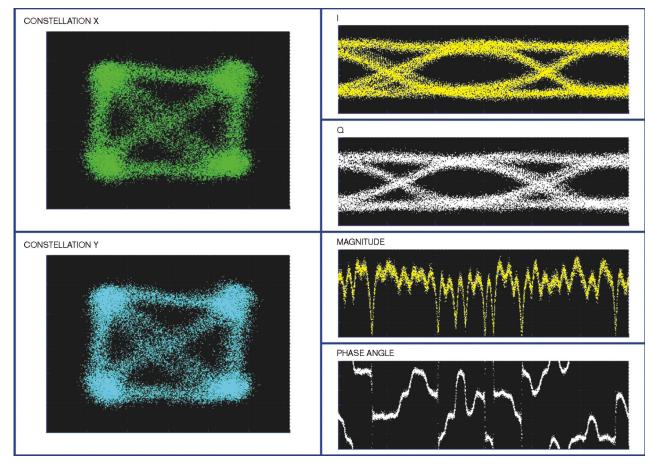

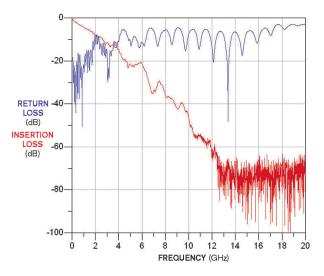

# Complex modulation comes to optical fiber

32 Fiber is running out of bandwidth just as dial-up lines did years ago. Complex modulation again solves the problem. *by Martin Rowe,* Test & Measurement World

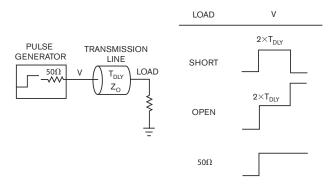

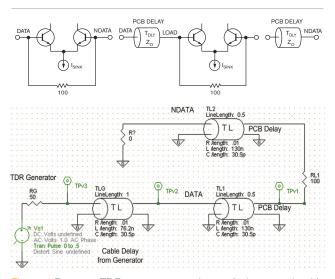

#### Measure propagation delays using timedomain reflectometry

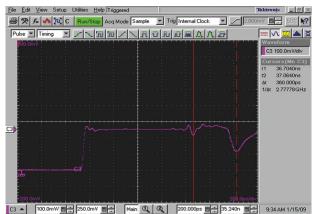

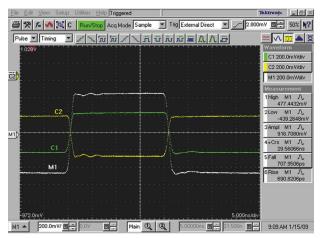

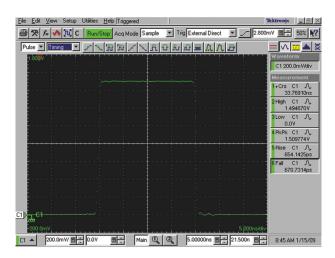

36TDR beats active probes for high-speed delay measurements.

> by Bernard Hyland, Maxim Integrated Products

#### Continuous-time equalizers improve high-speed serial links

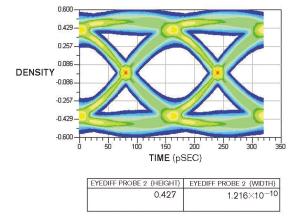

4 OYou can design an effective serial-channel equalizer in a few minutes. by Sanjeev Gupta, Agilent Technologies EEsof Division

# DESIGNIDEAS

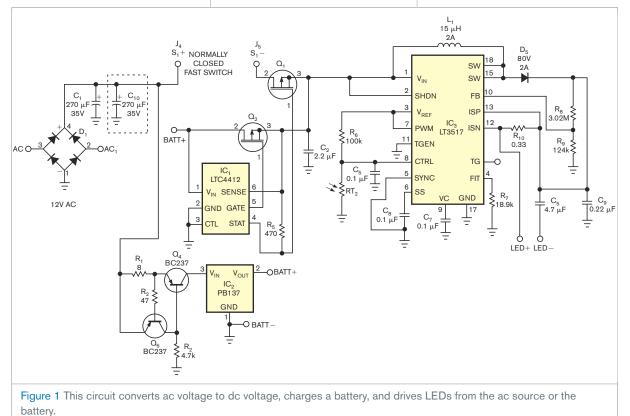

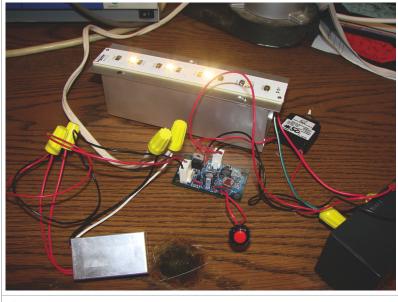

45 Efficient LED power supply has battery backup

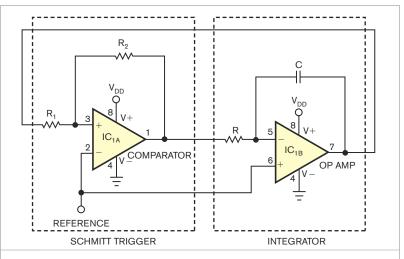

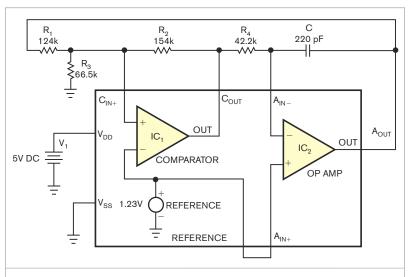

46 Single IC forms precision triangular-wave generator

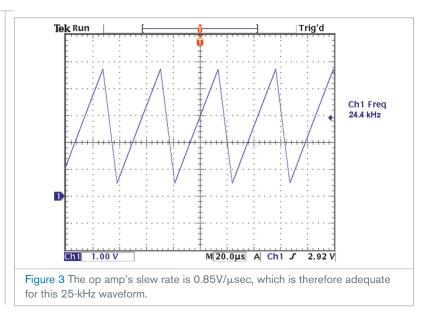

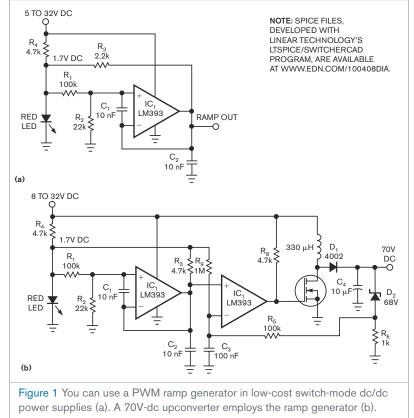

- 50 Use a low-cost PWM ramp generator in switch-mode power supplies

- 52 MSP430's port-interrupt-request logic helps debounce contacts

- > Send your Design Ideas to edndesignideas@reedbusiness.com.

### **DEPARTMENTS & COLUMNS**

- 4 **EDN.comment:** Lifetime and reliability in LEDs and why SOC designers should care

- 15 Signal Integrity: Manager's guide to digital design

- 56 Supply Chain: Distributors step up embedded-systems support

- 58 **Product Roundup:** Discrete Semiconductors, Computers and Peripherals

- 60 Tales from the Cube: Can't put a Band-Aid on a boomerang

### **EDN**) online contents

www.edn.com

#### ONLINE ONLY

Check out these Web-exclusive articles:

#### IC reverse engineeringa design-team perspective

The IC Insider explains the why and how of circuit extraction of semiconductor chips.

→www.edn.com/article/CA6722668

#### Circuit protection for outdoor LED lighting

Outdoor LED lighting can be an efficient, "greener" source of light in addition to promising a long, maintenancefree life. However, outdoor LED-lighting installations can be less reliable than conventional lighting unless designers add the proper circuit protection to guard against the most severe overvoltage conditions.

→www.edn.com/article/CA6721136

# INNO ATION

Voting may be over, but it's not too late to order tickets for the awards reception to be held April 26 in San Jose, CA. Be there when the winners are announced. →www.edn.com/ innovation

# IR's IRF6718 Delivers Industry's Lowest R<sub>DS(ON)</sub>\*

Optimized for Active ORing and Hot Swap Applications

#### Features

- Industry Lowest R<sub>DS(on)</sub> for reduced conduction losses

- Superior electrical and thermal performance in smaller footprint than D<sup>2</sup>Pak

- Dual-sided cooling compatible

- Reduces component count and board space compared to competing solutions

- Compatible with existing Surface Mount Techniques

- RoHS compliant containing no Lead or Bromide

| Part<br>Number | Package<br>Size<br>(mm x mm) | R <sub>DS(ON)</sub> @ 10V<br>typ. (mΩ) | I <sub>D</sub> @TA = 25°C<br>(A) |

|----------------|------------------------------|----------------------------------------|----------------------------------|

| IRF6718        | 7.1 x 9.1                    | 0.5                                    | 270                              |

| Competitor 1   | 10.7 x 15.9                  | 0.7                                    | 180                              |

| Competitor 2   | 5.1 x 6.1                    | 0.95                                   | 60                               |

| Competitor 3   | 5.1 x 6.1                    | 1.5                                    | 65                               |

\* Based on data complied September 2009

#### For more information call 1.800.981.8699 or visit www.irf.com

International **ICPR** Rectifier THE POWER MANAGEMENT LEADER

CA 90064-1549; 310/445-4200; FAX 310/445-4299. Periodicals postage paid at Los Angeles, California, and at additional mailing offices. SUBSCRIFTIONS—Free to qualified subscribers as defined on the subscription card. Rates for nonqualified subscriptions, including all issues: US, \$179.99 on eyar; Canada, \$229.99 on eyar; (includes 7% GST, GST#12337467); Mexico, \$229.99 one year; are xeptidet, \$399.99 one year; Except for special issues where price changes are indicated, single copies are available for \$10 US and \$15 foreign. For telephone inquiries regarding subscriptions, call 763/746-2792. Email: EDN0k/mpsgroup.com. CHANGE OF ADDRESS—Notices should be sent promptly to PO Box 47461, Pymouth, MN 55447. Pease provide old mailing labels as well as new address. Allow two months for change. NOTCE—Every precation is taken to ensure accuracy of content; however, the publishers cannot accept responsibility for the correctness of the information supplied or advertised or for any opinion expressed herein. POSTMASTER—Send address to EDN, PO Box 47461, Pymouth, MN 55447. Canada Post: Publications Mail Agreement 40685520. Return undeliverable Canadian addresses to FCS International. Box 697 STN A, Windsor, Ontairo N9A 6M4. Printed in USA. Copyright 2010 by Canon Communications LLC. All rights reserved. Reproduction in whole or part without written permission is prohibited.

EDN® (ISSN#0012-7515) is published semimonthly, 24 times per year, by Canon Communications LLC, 11444 W. Olympic Blvd., Los Angeles,

#### BY RON WILSON, EXECUTIVE EDITOR

### Lifetime and reliability in LEDs and why SOC designers should care

nt it w h b

ne of the wonderful things about this job is the chance to sit in on presentations unrelated to my beat. The subject of this commentary, a paper at *EDN*'s "Designing with LEDs" seminar, is a case in point. In 45 minutes, I heard some hard-earned lessons from a different world but with implications for SOCs (systems on chips). The

presenter, Geof Potter, is a power technologist at Texas Instruments. After a quick review of what goes into an LED-lighting assembly—basi-

cally, a power supply and a bunch of LEDs—Potter decomposed the luminaire assembly into its components and discussed the impact of each on lifetime and reliability.

The two terms are different in Potter's world. "Lifetime" refers to the length of service before the luminaire falls below some determined fraction of rated light output. "Reliability" refers to the probability that the luminaire will require repair or replacement during its rated life. It's possible, for example, for a luminaire to have a lifetime of 10 years but still require repairs every three weeks.

It seems obvious that the shortestlived, least-reliable component in the luminaire would be the LED. It turns out, though, that if you run the little guys conservatively and cool them aggressively, they will be fine. The next most obvious culprit is the fluid-filled aluminum electrolytic capacitors in the power supply. Everybody has had bad experiences with e-caps: aging, electrical degradation, and a distinctively bad aroma as they near end of life. According to Potter, however, when you use them conservatively, extended-life e-caps have a working

life that can exceed that of the LED assemblies.

Similarly, optocouplers have been problems in the past. But high-reliability couplers, properly used, will have more than adequate reliability. Cutting costs on these components or allowing an assembly house to make unauthorized substitutions will lead to trouble, however.

Once you've eliminated LEDs and e-caps as the worst problems, only solder joints remain. According to Potter, the 50-year-old problem has reappeared in LED lighting, and the reasons are unfortunately relevant to many SOC designs. The key issue is quality of soldering, Potter said. All solder joints age, and poor mechanical connection, contamination, or insufficient heating greatly accelerates this aging. The lighting market tends to be highly cost-sensitive, and it heavily outsources the supply chain to lowlabor-cost areas and those more familiar with mechanical assembly than electronics fabrication.

Furthermore, luminaires can live in high-stress environments. Think of an automobile headlamp's "eyebrow," that cute little string of white LEDs that makes this year's luxury sedans distinctive in the dark. The front of the car may be moving at 100 km/ hour into a  $-10^{\circ}$ C evening when the lamps come on, quickly self-heating to  $70^{\circ}$ C, all while enduring road shocks and engine vibrations.

Maybe Bosch is comfortable assembling a fixture for this environment, but is your low bidder in Southeast Asia? Potter's suggestions are to ensure manufacturing quality and minimize thermal and mechanical stress. These approaches may be largely beyond the control of the design team, however, so he stressed another point: Use the fewest solder joints that you can.

The SOC world also faces growing cost pressures, uncertainties about its customers' supply chains, and the need for designs to operate in hostile environments. Potter's data suggest that, by doing whatever is possible in the architecture and implementation of the system SOC to minimize the number of solder joints in the end system, you can have a dramatic impact on system reliability and on total cost of ownership. Ideas such as using the highest feasible level of functional integration, absorbing or eliminating the need for external passive components, and minimizing both the number of pins on the SOC and the number of lines that must pass through connectors are not just good practice. They are becoming differential advantages that can sell-or doom-an entire SOC family.EDN

Contact me at ronald.wilson@reed business.com.

#### PUBLISHER, EDN WORLDWIDE

Russell E Pratt, 1-781-734-8417; rpratt@reedbusiness.com

ASSOCIATE PUBLISHER, EDN WORLDWIDE Judy Hayes, 1-925-736-7617;

judy.hayes@reedbusiness.com EDITOR-IN-CHIEF, EDN WORLDWIDE

Rick Nelson, 1-781-734-8418; rnelson@reedbusiness.com

EXECUTIVE EDITOR Ron Wilson, 1-510-744-1263; ronald.wilson@reedbusiness.com

#### MANAGING EDITOR

Amy Norcross 1-781-734-8436; fax: 1-720-356-9161; amy.norcross@reedbusiness.com Contact for contributed technical articles

#### SENIOR ART DIRECTOR

Mike O'Leary 1-781-734-8307; fax: 1-303-265-3021; moleary@reedbusiness.com

ANALOG Paul Rako, Technical Editor

1-408-745-1994; paul.rako@edn.com

#### MASS STORAGE, MULTIMEDIA, PCs, AND PERIPHERALS

Brian Dipert, Senior Technical Editor 1-916-760-0159; fax: 1-303-265-3187; bdipert@edn.com

#### MICROPROCESSORS, DSPs, AND TOOLS

Robert Cravotta, Technical Editor 1-661-296-5096

#### NEWS

Suzanne Deffree, Managing Editor 1-631-266-3433; sdeffree@reedbusiness.com

#### POWER SOURCES, ONLINE INITIATIVES

Margery Conner, Technical Editor 1-805-461-8242; fax: 1-805-461-9640; mconner@reedbusiness.com

#### DESIGN IDEAS EDITOR

Martin Rowe, Senior Technical Editor, Test & Measurement World edndesignideas@reedbusiness.com

#### SENIOR ASSOCIATE EDITOR

Frances T Granville 1-781-734-8439; fax: 1-303-265-3131; f.granville@reedbusiness.com

#### EDITORIAL/WEB PRODUCTION

Diane Malone, Manager Steve Mahoney, Production/Editorial Coordinator Melissa Annand, Web Operations Specialist Adam Odoardi, Prepress Manager 1-781-734-8325; fax: 1-303-265-3042

> CONSULTING EDITOR Jim Williams, Staff Scientist, Linear Technology

CONTRIBUTING TECHNICAL EDITOR Dan Strassberg,

strassbergedn@att.net

#### COLUMNISTS

Howard Johnson, PhD, Signal Consulting Bonnie Baker, Texas Instruments Pallab Chatterjee, SiliconMap

#### PRODUCTION

Dorothy Buchholz, Group Production Director 1-781-734-8329 Joshua S Levin-Epstein, Production Manager 1-781-734-8333; fax: 1-781-734-8096

#### EDN EUROPE

Graham Prophet, Editor, Reed Publishing gprophet@reedbusiness.com

#### EDN ASIA Luke Rattigan, Chief Executive Officer luke.rattigan@rbi-asia.com Kirtimaya Varma, Editor-in-Chief kirti.varma@rbi-asia.com

#### EDN CHINA

William Zhang, Publisher and Editorial Director wmzhang@rbichina.com.cn Jeff Lu, Executive Editor jefflu@rbichina.com.cn

#### EDN JAPAN

Katsuya Watanabe, Publisher k.watanabe@reedbusiness.jp Ken Amemoto, Editor-in-Chief amemoto@reedbusiness.jp

#### **EXECUTIVE OFFICERS**

Charles G. McCurdy, Chief Executive Officer Daniel Koskovich, Chief Financial Officer Ron Wall, Senior Vice President, Publications Kevin O'Keefe, Senior Vice President, Events Division Roger Burg, Vice President, Operations Jason Brown, Vice President, E-Media

EDN. 225 Wyman St, Waltham, MA 02451. www.edn.com. Phone 1-781-734-8000. Subscription inquires: 1-763-746-2792; EDN@kmpsgroup.com. Address changes: Send notice promptly to PO Box 47461, Plymouth, MN 55447. Please provide an old mailing label as well as your new address. Allow two months for the change. Canon Communications LLC, 11444 W. Olympic Blvd., Los Angeles, CA 90064-1549; 1-310-445-4200; fax: 1-310-445-4299.

# **RELIABILITY**

Mill-Max Mfg. Corp. spring-loaded connectors provide superior reliability under the most rigorous environmental conditions, offering:

- Continuous, low-noise electrical connections.

- Spike-free stability to 50G shock and 10G vibration.

- Continued high performance

- through 1,000,000+ cycles.

- Low- and high-profile surface-mount styles.

- 45 discrete designs for customer-specific assemblies.

- 6 families of single and double strip assemblies.

- The shortest production lead times in the industry.

SLC Connector Assemblies

#### Stay in contact with Mill-Max spring-loaded connectors.

To view our Design Guide, new product offerings and request a datasheet with free samples, visit

MILL-MAX

www.mill-max.com/EDN596

# MEET THE GUY that ELIMINATED HIS TEAM'S MANUFACTURING VARIABILITY ISSUES.

FIX YOUR MANUFACTURING VARIABILITY PROBLEMS AND YOUR REPUTATION WILL PRECEDE YOU. If you're designing chips for high functionality, high speed and lower power consumption at the most advanced process nodes, you've got variability issues. We have the solution that will increase your yield, performance and prestige by a wide margin. Get more information at mentor.com/solutions/manufacturing-variability.

#### EDITED BY FRAN GRANVILLE

#### **INNOVATIONS & INNOVATORS**

# Expandable 3.6-, 6-, and 13.5-GHz signal analyzers feature optional built-in generator

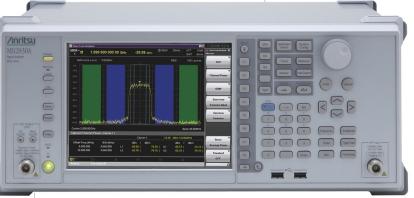

A nritsu has introduced the MS2830A signal analyzers, which deliver best-inclass speed and accuracy, according to the manufacturer, over a frequency range of 9 kHz to 3.6, 6, or 13.5 GHz in a cost-effective package. Focusing on applications in system integration and production, the new units enable manufacturers of third- and fourthgeneration wireless devices and systems to reduce manufacturing costs and increase both product yields and confidence in product performance.

The base model conducts frequency switching and sweeping and transfers batched measurement results in approximately 12 msec. If you install the VSA (vector-signal-analysis) option, the instruments support noise averaging in approximately 0.1 second, several times as fast as do conventional swept-frequency spectrum analyzers. In a 31.25-MHz analysis bandwidth, the VSA option's FFT-based batchcapture capability greatly increases the speed of inband measurements, such as channel power, adjacent-channel power, and one-box tester.

The high speed does not compromise accuracy: The average noise level without preamplification is -153 dBm at 1 GHz; tertiary phase-intermodulation distortion (third-order intercept) is 15 dBm, and typical total level accuracy is  $\pm 0.3$  dB. The instruments also perform precise distortion and spurious-frequency measurements. The MS2830A has measurement capabilities that previously required both a spectrum analyzer and a signal generator.

An optional built-in signal generator creates a one-box tester that performs transmitter and

receiver tests. With everything in one chassis, the resulting configuration costs as much as 30% less than a discrete signal analyzer and signal generator. In addition, the MS2830A consumes no more than 110W, which is 45% less than the power consumption of comparable signal analyzers.

You can customize the units to meet your current test requirements and perform simple and cost-effective upgrades when those needs change. The manufacturer offers such options as a VSA and a vector-signal generator. The new units are compatible with the manufacturer's application software that allows you to configure an analyzer to conduct quality analysis on LTE (long-term-evolution), W-CDMA (wireless code-division/multiple-access)/HSDPA (highspeed-downlink packet access), GSM (globalsystem-for-mobile-communication), and other wireless signals. The base MS2830A sells for \$14,200.-by Dan Strassberg

Anritsu Co, www.anritsu.com.

- FEEDBACK LOOP "The big, red E-Stop button may not bring about a smooth and dignified stop, but it will cause a stop in spite of any software failure or failures. ... Toyota could have done as well as we do, if it had just been willing to spend a small amount more."

-Engineer William Ketel, in EDN's Feedback Loop, at www. edn.com/article/CA6720350. Add your comments.

Cost-effective MS2830A signal analyzers, which feature bandwidths from 9 kHz to 3.6, 6, and 13.5 GHz, offer an optional built-in signal generator and a vector-signalanalysis option that batches measurement results, greatly speeding throughput.

# pulse

# Vitesse zeros in on carrier-Ethernet switch needs

he explosion of interest in CE (carrier Ethernet) seems to be at the front of everyone's mind these days. In case you haven't been following the networking market lately, the basic story is this: Just as wireless service providers and conventional telephone-service providers decided to evolve from their legacy switched networks and synchronous rings into Internet-compatible packet networks, they faced a coincidence of three massive trends: the explosion of data traffic in cellular networks, the allure of delivering high-definition television through IP (Internet Protocol) packets to homes, and the rumor of a huge shift toward cloud computing.

The result for both wireless backhaul networks and the wired infrastructure behind all those DSL (digital-subscriber-line) and cable connections was the same. The providers want a packet-based network with enormous bandwidth-such as enterprise Ethernet-but with all the features these providers had from their legacy networks. These services include awareness of the service needs of each flow through the switch, multicast capability, carrier-class reliability and management functions, and support for precise timing. Carriers also want to provide guaranteed QOS (quality of service) for media types such as voice and high-definition video. The answer to all these desires, the industry claims, is CE.

The next question is how to implement CE in a way that can be both fast and cheap. Service providers are blowing right past 40-Gbit switches and asking for 100-Gbit capability, but they are severely financially constrained. The obvious solution is to start with a fast enterprise switch and enhance it to provide the additional services. This approach runs into problems, however.

If your enterprise switch relies on NPUs (network-processing units), you can simply add to the NPU software, but you will almost certainly run out of processing power long before you get all the new features in, even at low wire speeds. If your switch uses an ASSP (application-specific standard product) or an ASIC, it won't be flexible. Either way, you will have to add another ASIC or, more likely, an FPGA or two to the design, running up the BOM (bill-of-materials) cost, power, and design time.

Service providers are blowing past 40-Gbit switches and asking for 100-Gbit capability, but they are financially constrained.

And, as Morteza Ghodrat, director of CE technology at Vitesse Semiconductor, is quick to point out, adding more packet-processing sites to the design means adding more DRAMs and CAMs (contentaddressable memories). Either you put duplicate memory chips around each chip, or you attempt some sort of sharedmemory pool with the obvious complications.

To address these problems, Vitesse recently announced three MAC (media-accesscontroller) and switch chips. Ghodrat argues that all CE services interrelate both architecturally and in efficiency; thus, a single architecture rather than multiple chips should handle them. The new ASSPs, the VSC7460 Jaguar CE switch, the VSC7462 LynX CE switch, and the VSC7364 CE-MaX-24 MAC/switch, bring the full range of CE functions to highspeed Ethernet switches.

Accordingly, each chip has a service-aware classifier that can manage as many as 4000 services, each with its own QOS treatment, DE (discard-eligible) marking, color, policing, OAM (operations/ administration/management), performance monitoring, and timing support through IEEE 1588 Version 2. The chips provide advanced QOS and MEF (Metro Ethernet Forum) policing based on a shared 32-Mbit buffer. They also have statistics counters: Ethernet OAM for all 4000 services; and support for 802.1ag, 802.3, Y.1731, and MEF-16 performance assurances.

The chips differ in CPU and I/O complements. The Jaguar has two 10-Gbps XAUI (10-Gbps attachment-unit-interface) and two 10-Gbps VAUI (5-Gbps-attachment-unitinterface) ports on one side and 24 multifunction SGMII (serialgigabit-media-independentinterface)/SERDES (serializer/deserializer)/100BaseFX ports on the other. The LynX has just half as many of each. Both devices include a 400-MHz MIPS24KEc processor core.

The CE-MaX chip, which operates with an ASIC or an FPGA, uses two XAUI ports and a host interface to attach to the other chip and provides the full 24 SGMIIs plus two more XAUI ports downstream. The CE-MaX has no on-chip CPU. All three chips will be available in  $27 \times 27$ -mm HSBGA packages, and all are scheduled to become available for sampling in the second quarter.

#### -by Ron Wilson

▷Vitesse, www.vitesse.com.

#### **DILBERT By Scott Adams**

# Single-key capacitive touch controllers target use in portable products

A the las incorporated the technology of its OTouch charge-transfer capacitive touch sensors into a series of single-key touch controllers for the portable-device market. Applications extend beyond touch keys for single-button mechanical-switch replacements to a range of body-proximity-sensing scenarios. The chips have a power consumption of less than 17  $\mu$ A at 1.8V in low-power mode and a fast wake-up time. From

the low-power state, when these devices detect a key touch, they temporarily switch to a 12.6-msec fast-response mode, allowing rapid detection of additional touches.

As with other related parts, the AT42QT101X family uses spread-spectrum modulation to ensure good EMC (electromagnetic compatibility). The ICs automatically calibrate when you power them up and remain calibrated, even with moisture buildup

The AT42QT101X family of capacitive touch sensors target use in body-proximity-sensing scenarios.

#### There are few constraints on key shape or size.

or other contaminants on the touch surface.

The family comprises the AT42QT1010, AT42QT1011, and AT42QT1012. The 1010 part includes a timer to reset a "stuck-key" condition: After 60 seconds, it powers down, resets, and self-calibrates to an assumed untouched state. The 1011 remains in the "touched" condition indefinitely when it senses a contact; this feature allows uses such as detecting when an earpiece of a headset is in the user's ear canal or detection of face proximity in a smartphone. The 1012 includes a touch-on/touch-off,

or toggle, key and a configurable power-down timer to shut down devices that users inadvertently leave on.

Users can configure the key sensitivity on all devices for different panel thickness and materials. Electrodes can consist of any conductive material, including transparent indiumtin oxide. There are few constraints on key shape or size, allowing the user a great level of flexibility in the industrial design. The user can also set up the IC for use as a proximity sensor, allowing detection of a nearby hand or object. Toys typically have this function to illuminate "hidden-until-lit" keys when a hand or a finger approaches a consumer appliance. The devices come in a 2.9×1.6-mm SOT-23 package and need only two external components. Prices start at 20 cents (volume guantities).

-by Graham Prophet

Atmel, www.atmel.com/

products/touch.

04.08.

#### 3-D HOLOGRAPHIC IMAGES DELIVER IMPRESSIVE REALISM, NEED NO GLASSES

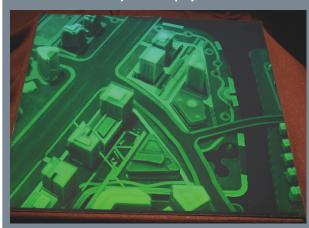

Zebra Imaging has developed 3-D holographic images that can replace expensive, bulky, and time-consuming models at construction sites. You can put these displays into a briefcase, hop onto a plane, and show the on-site construction foreman just how a project should look.

Zebra Imaging's 3-D holographic images can fit into a briefcase and replace bulky models at construction sites.

The company burns each image into photopolymer film with intersecting laser beams. Each holographic image starts with a 3-D digital model. If no such model exists, the company can create it by scanning geospatial terrain, digitizing an object, or creating a digital model from scratch using computer graphics or engineering software.

For geospatial applications, terrain data may exist for a region of interest. For architecture and other applications, Zebra accepts many 3-D digital file formats, including those exported by Catia, Maya, Alias, 3D Studio Max, and AutoCAD software. After Zebra receives a 3-D digital model, the customer specifies the size, color, flexibility or rigidity, and opaque- or transparent-mounting options for the hologram.

Imaging times for  $2\times 2$ - and  $2\times 3$ -foot tiles are approximately two and three hours, respectively. The cost of a hologram depends on color, quantity, and size. Prices start at \$499 for a  $12\times 12$ -in. hologram, \$699 for a  $12\times 18$ -in. version, and as much as \$1999 for a  $24\times 36$ -in. hologram. Zebra can also mass-produce the images.

-by Margery Conner Zebra Imaging, www.zebraimaging.com.

# pulse

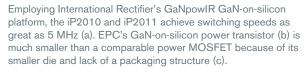

### GaN power transistors take aim at MOSFETs

R (International Rectifier), the first to build GaN (gallium-nitride) devices on silicon, has now introduced GaNpowIR, its first product on a GaN platform. GaN-device structures are not new; using a sapphire substrate, they've been around for 20 years in the RF realm. IR has, however, figured out how to make the ultrafast switching of GaN commercially viable for power electronics.

Consider the impact that hexagonal MOSFETs, the first commercially viable MOSFETs, had on the power semiconduc-

tor: According to Mike Briere, PhD, the company's technology consultant, the devices made possible the commercial manufacture of high-volume switching power supplies. The figure of merit for the deviceson-resistance times gate charge-has improved approximately two orders of magnitude over the past 30 years. This rate of improvement can't go on forever, Briere says. He envisions a scenario in which GaN-on-silicon technology will take over

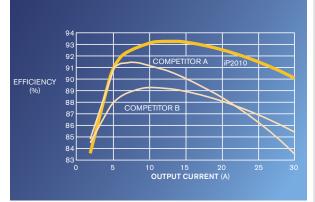

Enter IR's new iP2010 and iP2011 GaN-on-silicon-tech-

(a)

ate in native depletion mode, although they can operate in enhanced mode and switch at speeds as high as 5 MHz. The company's road map calls for devices to span 20 to 1200V. The devices integrate a powerstage device that includes a PowIRtune driver IC and a multiswitch monolithic GaNbased power device, all in a flip-chip package, that the company claims more than doubles the switching frequency of the devices.

nology devices, which oper-

The iP2010 operates at speeds as high as 3 MHz and features an input voltage range of 7 to 13.2V, an output voltage range of 0.6 to 5.5V, and an output current as high as 30A. Operating at speeds as high as 5 MHz, the pin-compatible iP2011 features the same input and output voltage ranges and an output current as high as 20A. By offering multiple current-rating devices in a common footprint, the devices meet customer requirements in current level, performance, and cost. The parts target the server power-supply market, in which some customers are willing to pay a hefty premium for power efficiency. Prices for the iP2010 and iP2011 begin at \$9 and \$6 (2500), respectively.

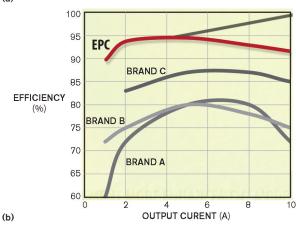

Hot on the heels of the IR announcement comes a new family of power transistors from

start-up EPC (Efficient Power Conversion). The company based the devices on its proprietary GaN-on-silicon technology. Their drain-to-source voltages range from 40 to 200V, and on-resistances range from 4 to 100 m $\Omega$ . The company claims that GaN devices can reduce total server-power requirements, including ac/dc and dc/dc losses and fans, by about 18%.

EPC developed the GaN technology with a normally off enhancement mode explicitly to replace power MOSFETs. According to Alex Lidow, EPC's co-founder and chief executive officer, enhancement mode, rather than depletion mode, is essential for GaN to become a broad-scale siliconpower-MOSFET replacement. "It's meant to imitate the functionality of a power MOSFET on supersteroids," he says. Because EPC can lay down the GaN structures on standard 6-in. wafers, its prices-80 cents and \$5 (1000)-are comparable to those of highend MOSFETS. The parts are available from Digi-Key (www.digikey.com).

The on-resistance for a device area is a key determinant of cost, and a GaN transistor is markedly smaller than an equivalent MOSFET. Unlike MOSFETs, EPC's transistors lack a packaging structure. The hermetically sealed GaN elements lie atop the silicon layer, which acts as an insulator. You can mount the GaN transistor directly on a heat sink with no surrounding packaging and no thermal resistance between the transistor and its package.

-by Margery Conner ▷International Rectifier, www.irf.com. ▷Efficient Power Conversion Corp, www. epc-co.com.

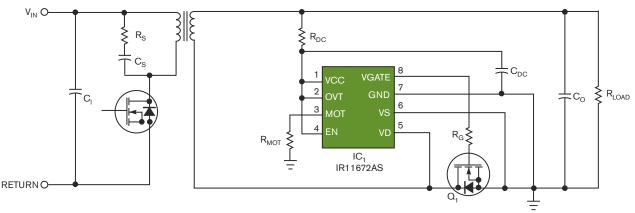

# Smart FET driver emulates rectifier in secondary-side applications

nternational Rectifier's new IR11672 synchronous-rectification IC drives a MOSFET in the secondary side of an ac/ dc flyback and resonant halfbridge switched-mode power supply, providing the function of a rectification diode. The FET's forward-voltage drop is smaller than that of a Schottky diode. You connect an input comparator across the power MOSFET, enabling it to sense the direction of the rectified current. The IC operates from an 11.3 to 20V power supply, and its drain-sense pin can withstand 200V. Maximum switching frequency is 500 kHz, turn-off propagation delay is 50 nsec, and turn-on delay is 60 nsec. The device provides peak FET-gate turn-off drive current of 7A, and the unit has both an enable pin and a gateoutput pin with a 10.7V clamp circuit.

In addition to conventional gate-drive circuitry, the IR11672 contains minimumon-time circuitry that blanks the comparator's input to prevent spurious ringing and oscillation from turning the part off. This feature guarantees proper operation in continuous-, discontinuous-, and critical-conduction modes. The IR11672 provides secondaryside synchronous rectification in switch-mode power supplies. It comes in an eight-pin SOIC package, operates in the −40 to +150°C temperature range, and sells for 92 cents (10,000).-by Paul Rako ▶International Rectifier, www.irf.com.

The IR11672 and a FET replace the diode in a power supply's secondary.

#### SHARP EXPANDS ITS REPERTOIRE OF LCDs FOR IN-CAR USE

The display-research arm of Sharp Electronics has revealed some of its advanced work exploring options in LCD technology for automotive use, including an enhanced version of its dual-view LCD panel and a dual-depth panel that shows information on two visual planes. Sharp supplies its dual-view panels to two car manufacturers, which install them in the center console of the dashboard. The dual-view panel shows two separate images when you view them off-center from either side of the display. In the automotive application, the driver can see only relevant information, such as navigation or carsystem menus, while the front-seat passenger views entertainment content. In the first generation of panels, now in production, Sharp achieves the image separation with a parallax barrier: The two images appear on interleaved vertical pixel strips, and a vertical linear grating in front of the screen obscures the set of pixel strips corresponding to the "hidden" image on the respective side.

Now, Sharp has developed an enhanced version of the screen, which may use microlens arrays rather than an aperture grating. This approach allows the company to

tune the performance to different use cases; you can have twice the brightness of the previous version at the cost of a somewhat wider region of "mixing"–that is, the viewer sees both images superimposed. Alternatively, you can achieve almost no region of mixed images but with similar brightness to that of the first-generation panels.

The second innovation is a dual-depth panel, which has two distinct visual-image planes that appear at different distances. The optics involve a standard panel with a layered arrangement of optical planes, including a partially reflecting mirror and polarizers, in front of it. The light path through the extra optics is electrically switchable. In one state, light passes straight through, and the viewer sees the LCD screen directly. In the alternative state, light from the panel internally reflects within the arrangement of polarizers before exiting in the direction of the viewer. The optical-path length is increased by twice the thickness of the polarizer/mirror-assembly layer, and the image therefore appears to be displaced backward by that amount.-by Graham Prophet

Sharp, www.sharpsme.com.

# pulse

### Rethinking static-timing analysis

TA (static-timing analysis) was nearly an instant success at timing closure 15 years ago, and nothing much has changed since except for creating partitioning/scheduling algorithms to parallelize the algorithms for multicore CPUs. This stasis has allowed an increase in the number of instances in a design, the number of modes in which you must analyze a design, and the number of process corners. Consequently, runtimes for full designs across modes and corners have become enormousdays, in some cases.

That situation has turned STA from an elegant, fast tool into a powerful and trusted, but ponderous, necessity, consuming licenses and days of precious schedule with abandon. If there were a way to dramatically speed up STA, users would need fewer licenses, could save the real-estate and power costs for huge server collections, and could employ the tool in situations in which it has become impractical today, such as checking timing constraints or evaluating ECOs (engineering change orders).

Several alternatives exist for accelerating STA. To begin with, the task is parallelizable. Most nets are independent with regard to delay, so you can organize the nets into independent sets and dispatch them to independent threads. That fact makes STA inherently friendly to multicore computing and, more practically, to execution on graphics processors.

According to Dan Blong, technical-marketing manager at Magma Design Automation, 15 years have elapsed since anyone looked at the underlying algorithms and the code to see whether there were other ways to accelerate the analysis. A team headed by Pathmill pioneer Jacob Avidan set out two years ago to accomplish

#### An incremental mode lets you work directly on particular blocks of IP.

that goal. The result is Tekton, a new STA/extraction/Spice environment. Magma claims that Tekton runs significantly faster as a timing analyzer on a single CPU and dramatically faster in a multimode/multicorner analysis on a multicore machine. The company claims that it can perform these tasks on any design, using one machine, and in less than an hour, further claiming a speed of 1 million nets per minute and near-linear scaling for as many as 24 CPUs.

The improved performance comes primarily from care-

ful organization of the work to avoid the need for repeating calculations—that is, recognizing tasks that are unnecessary and saving intermediate results for use in future calculations. It does not mean compromising timing accuracy. Blong says that Tekton correlates well with PrimeTime delay results and approximates PrimeTime crosstalk results.

Tekton drops into existing flows, accepting PrimeTime tcl and Perl scripts. The complete Tekton environment includes the Tekton QCP extraction tool, which correlates to QuickCap, and crosstalk analysis, on-chip variation analysis, and an integrated Spice engine. In addition to timing an entire design in less than an hour, the package includes an incremental mode that lets you work directly on particular blocks of IP (intellectual property) or on ECOs.

-by Ron Wilson ⊳Magma Design Automation, www. magma-da.com.

-by Ann Steffora Mutschler

#### INTEL UNVEILS 32-nm DATA-CENTER MICROPROCESSORS

Aiming to provide data centers with a stronger foundation for cloud security, Intel recently announced its Xeon 5600 series, which combines security, performance, and energy-efficient features, according to the company. The processors contain Intel's AES-NI (Advanced Encryption Standard-new instructions), which Intel introduced with the Core processor family. These instructions accelerate AES performance to allow faster data encryption and decryption for applications such as database encryption, full disk encryption, and secure Internet transactions. The processors also feature TXT (trusted execution technology), which allows faster encryption and decryption performance for more secure transactions and virtualized environments. These workstation and server chips use the company's 32-nm logic technology, which employs Intel's second-generation, high-k-metal-gate transistors to increase speed and decrease energy consumption.

The devices allow as many as six cores to reside on each processor and can deliver as much as 60% greater performance than the 45-nm 5500 series. Intel claims that data centers using the new devices can replace 15 single-core servers with one. A two-socket server using the new series' low-voltage L5640 can deliver the same performance as but consume as much as 30% less power than a server using the previous generation's X5570 series. The processor also integrates TXT-hardware features that prohibit intrusion from malicious software, allowing applications and data to run more securely in a virtualized environment. Together, these features ensure that virtualized environments experience better performance and are more secure when users deploy or migrate them.

The frequency-optimized quad-core version of the 5600 series offers a maximum speed of 3.46 GHz with a total power dissipation of 130W, and the six-core version reaches 3.33 GHz with a power dissipation of 130W. Advanced six-core versions will top out at 2.93 GHz and 95W, and the standard quad-core processor will reach 2.66 GHz and 80W. Low-voltage versions of the chip will have power dissipations as low as 60 and 40W and feature six and four cores, respectively.

Intel Corp, www.intel.com.

## Technical Notes The Avago Advantage

### Avago Fiber Optics: Breaking Bandwidth and Performance Barriers in Supercomputing

#### Introduction

Modern datacenters, high-performance computing (HPC) centers, and supercomputers demand dense highbandwidth cost-effective interconnect solutions for the fabric between various computing resources and network elements. The bisection bandwidth of this fabric is a key factor in determining the overall performance of the system. As applications (internet search, cloud applications, complex computations, virtualization) and hardware (faster multicore processors, more I/O per server) put more demands on resources, the fabric bandwidth must scale as well.

Parallel interfaces, which can be either electrical or optical, provide a convenient means to achieve these interconnects. In contrast to single-channel connectors, parallel interfaces contain multiple lanes in a single electrical or optical connector. Logically, the interface can be a collection of coupled lanes that provide an aggregate channel bandwidth that is not achievable with serial technology (4xQDR Infiniband provides 40Gbps of aggregate channel bandwidth using four 10Gbps lanes) or a collection of individual single-channel interfaces (such as the fabric of a multistage switch/router). The interface can also be a combination of the two (three 4xQDR channels on one 12-lane interface).

As lane speeds move to 10 Gbps and beyond, fiber-optic technologies are displacing copper-based solutions that have long dominated these parallel interfaces. Fiber optics offer distinct advantages in density, power, weight, and link length. However, a thorough understanding of the benefits of fiber optics over copper goes beyond these simple metrics. Architects can choose where to deploy dense parallel optics solutions to achieve the optimal I/O bandwidth density: rack-to-rack, within a rack, and within board. In this technical note, we review various parallel optical technologies and then focus on embedded solutions developed by Avago that uniquely enable our customers to bring differentiated systems to market.

#### **Pluggable parallel optics**

Today, parallel-optical modules are widely available in two formats: pluggable and embedded. Pluggable modules are applicable when the aggregate I/O requirements of a system can be accommodated by the limited front-panel area. Common packages include QSFP (4-lane interface) and CXP (12-lane interface) with line rates running up to 12.5 Gbps. Examples of these form factors are shown in Figure 1. The advantages of the pluggable solutions include pay-as-you-grow deployment, choice of copper and optical options, and ease of assembly. However, density, thermal, EMI, and signal integrity challenges sometimes lead to tradeoffs in system performance in order to accommodate the pluggable format.

Figure 1: Avago AFBR-79Q4Z QSFP and AFBR-83BDZ CXP pluggable parallel transceiver modules.

#### **Embedded parallel optics**

Avago Technologies is the market leader in delivering embedded parallel optics for applications such as the fabric between chassis in multi-chassis routers/switches and highperformance computing clusters. Historically, the dominant form factors have been SNAP12 and POP4, with speeds up to 3.125Gbps per lane. Avago has extended the bandwidth capability to as high as 10 Gbps per lane. These modules can be mounted at the card edge as well as mid-board to optimize their placement for signal integrity and air-flow. In the latter case, fiber jumper cables are used to provide the optical interface to the panel. The use of high-density optical connectors, such as 24-, 48-, and 72-ferrule MTP™, enables single ports with extreme amounts of bandwidth. For example, a 72-ferrule MTP connector with each lane running at 10 Gbps can provide a 360 Gbps bidirectional interface in less than 1 square inch of panel area, equivalent to the connectivity provided by three CXP modules.

Figure 2. The MicroPOD, Avago's next-generation embedded parallel-optics module and optical connector shown with a dime for scale.

Next-generation computing, switching, and routing systems will require Terabytes of interconnect between nodes. In order to accommodate pluggable solutions, all of the I/O must be routed to the front panel. Even if edgemounted optics could provide sufficient density, significant signal integrity and thermal challenges would need to be overcome and the number of individual connections would be cumbersome. Embedded parallel optics can provide a solution, but legacy form factors (POP4 and SNAP12) are large and require keepout areas for the MTP connectors. To address higher density applications, Avago has introduced a novel parallel optics module, called MicroPODs (Figure 2), with unprecedented density (7.8 mm x 8.2 mm for 12 channels). The 12-channel transmitter and 12-channel receiver modules nominally operate at 10 Gbps per lane (120 Gbps aggregate bandwidth). A top-attached optical connector with a convenient slot for fiber routing permits dense tiling of the MicroPODs (Figure 3). At the card edge, high-density optical connectors can be used for consolidated I/O. For high-speed signal integrity, a µLGA electrical connector is used to mate the module to the host. The module includes such features as programmable perlane equalization and de-emphasis as well as a full set of diagnostic monitoring capabilities.

Figure 3. A densely tiled group of 8 MicroPOD Tx/Rx pairs provides a total bidirectional bandwidth of (960 + 960) Gbps in less than 3 square inches of board area.

#### Application example: High-performance computing

High performance computing has allowed advances in a wide variety of areas, including climate modeling, drug design, car crash studies, oil reserve discovery and computation-based business strategies. Businesses, education and research institutions, and governments increasingly rely upon HPC to provide timely answers to computationally intensive analysis and design problems. HPC and supercomputer manufacturers are striving to improve the performance of these machines to address these applications.

HPC and supercomputer systems are clustered networks of computing resources. The connectivity between computing nodes, or interconnect bandwidth, is an important factor in determining the useful computational power of the system. As individual processors increase in computation capability, the interconnect bandwidth between nodes of the cluster must scale to achieve the desired system performance. Where individual processor cores today may have 1 - 10 Gpbs of connectivity bandwidth to the fabric, next generation systems will require 10s to 100s of Gbps per core. Furthermore, many processor cores can reside in one node, requiring 10's of Tbps of connectivity from each node. Pluggable solutions cannot achieve this scale of bandwidth, considering the difficulties of routing 1000's of high speed lanes to the card edge as well as real-estate limitations.

Avago's MicroPOD technology alleviates the I/O bandwidth escape limitations imposed by front-panel mounted parallel optics. Supercomputer architects have freedom to scale the bandwidth of the inter-processor communications to optimize system performance with limited restrictions on the I/O bandwidth. For example, a 1 Teraflop node with ~2 Tbps/sec of connectivity to the network would require 16 Tx/Rx MicroPOD pairs. These modules would be positioned near the host IC for optimal signal integrity while also arranged in a tiling pattern for density. Using highdensity MTP connectors at the front-panel, the I/O could be consolidated into ports that have the ideal bandwidth for node-to-node communications. The area required for these ports would be significantly less than that required for a similar CXP-based interface.

Additionally, whereas the CXP must be mounted in the plane of the host PCB, the passive MTP connectors could be arbitrarily positioned for optimal density and fiber management. These benefits of using MicroPOD can enable more processing power to be packed onto one physical compute node, thereby conserving valuable space and power in the data center.

#### Summary

Increasing demands on data centers and computational facilities are driving requirements for connectivity between computing resources. Pluggable solutions such as QSFP and CXP can address some of these applications, but very dense I/O requirements are best met with embedded optical solutions. Avago has addressed this market need with a novel parallel-optics module, the MicroPOD. The MicroPOD enables true system differentiation by relieving performance-restricting bandwidth bottlenecks.

Contact us for your design needs at: www.avagoresponsecenter.com/401

Avago, Avago Technologies, and the A logo are trademarks of Avago Technologies in the United States and other countries. All other trademarks are the property of their respective companies. Data subject to change. Copyright © 2010 Avago Technologies

SIGNAL INTEGRITY

#### BY HOWARD JOHNSON, PhD

# Manager's guide to digital design

This article is for all those hardworking engineering managers who just want a simple, one-page summary of everything they need to know about digital design.

**GROUND:** mythical electrical object that absorbs unlimited quantities of electrical current. Ground exists in Spice but nowhere else. Radar engineers in the 1930s discredited the concept of ground as anything more than a good place to grow carrots and potatoes.

**PARASITIC EFFECT:** a mysterious circuit effect that persists despite your best attempts to either eradicate it or blame it on a previous designer.

**RISE TIME:** rate of ascent through management ranks. Rise time may be sluggish or, in the case of an over-ambitious candidate, subject to wild overshoot and gyration.

**EQUALIZER:** the Chuck Norris of serial-transmission circuits. An equalizer improves the odds of success for all good bits by knocking out the bad artifacts. Just saying you have an equalizer makes investors swoon.

**ADAPTIVE EQUALIZER:** Chuck Norris with brains.

#### **DECISION-FEEDBACK LOOP:**

a critical management decision made, then retracted, and then made again in a repeating loop. This loop knocks productivity to zero.

**HEAT SINK:** a small metallic device attached to your CPU that, like

Figure 1 The author visualizes his next great product, or is he just fooling?

the cooling tower at a nuclear-power plant, is the only device standing between safe, reliable system operation and total core meltdown.

**NETWORK ANALYZER:** an expensive piece of gear that always reports bad news. When interviewing new hardware-engineering candidates, always say that you have one. Later, if that employee misbehaves, threaten to make him use it.

**INDUCTOR:** a two-terminal component, which, like a financial derivative, causes huge spikes followed by systemic crashes. Avoid speaking with engineers for at least two days if they mention the words "inductor" and "Spice" in the same sentence.

**DE-EMBEDDING:** the insomnious effect of a difficult measure-

ment problem that consumes copious amounts of overtime, often late at night, preventing normal sleep.

#### **POWER-SUPPLY DROOP:** a

diminution in the output of a healthy power supply when engaged in vigorous activity. An insufficiently turgid power supply droops to the point of ineffectiveness. No pill cures that condition.

**BOOT TIME:** the interval of time between your decision, based on how slowly your product runs under reallife conditions, to fire your chief software engineer and the moment his feet hit the pavement outside your building.

**SSO** (simultaneous-switching-output) noise: a feature. IC manufacturers believe that only by skimping on the number of power and ground pins can they offer high-speed IC products in inexpensive packages, thereby transforming SSO noise from a problem into a feature.

**ROHS** (restriction-of-hazardoussubstances) Lead-Free Solder Initiative: Evil plot by Luddites to rid the world of computers by first rendering all electronic products flaky and unreliable. The initiative may precipitate the collapse of Western civilization. Until then, just smile and go along with the scheme like everyone else.

**VISUALIZATION:** a mental process. More than any other group, hardware engineers must visualize a solution to every problem, which they do with their eyes closed. You may hear noises that sound like ordinary snoring but actually indicate a deep state of complete concentration. Never interrupt an engineer engaged in visualization (Figure 1).EDN

Howard Johnson, PhD, of Signal Consulting, frequently conducts technical workshops for digital engineers.

### "How can I tell if a power supply is reliable?"

### There's an indicator on the front.

It says "Agilent." With a typical MTBF of 40,000 hours, over half-acentury of experience, and with more than 250 models to choose from, Agilent's power supplies are the ones you can count on. In fact the array of our power supplies is so extensive, it wouldn't fit on this page. For clean, low-noise, programmable power to countless DUTs, there's an Agilent power supply with your name on it. Actually, it's our name on it, but you know what we mean.

> For free measurement tips and the Agilent Power Products brochure go to www.agilent.com/find/powertips

Agilent and our Distributor Network Right Instrument. Right Expertise. Delivered Right Now.

© 2010 Agilent Technologies, Inc.

Buy from an Authorized Distributor www.agilent.com/find/distributors

### **Agilent Technologies**

AS LTE NETWORKS ROLL OUT THIS YEAR, ENGINEERS WILL BE APPLYING VARIOUS TEST SCE-NARIOS IN LAB AND SMALL-SCALE FIELD TESTS TO THE LTE DEVICES AND EQUIPMENT THEY ARE DEVELOPING.

BY REINER GOETZ, ANNE STEPHAN, AND MEIK KOTTKAMP, ROHDE & SCHWARZ

s part of the worldwide 3GPP Release 8 standard, LTE has been fully defined since March 2009. This new technology is an essential enhancement of classic mobile-communications technologies, such as GSM/ EDGE, WCDMA/HSPA(+), and CDMA2000/Ev-Do Rev A. It promises end users significant data-rate, network-capacity, and latency improvements. LTE will also enable network operators to more effectively and inexpensively deliver services, such as Web browsing, gaming, and video streaming, and it will open the door for new mobile services.

Consequently, no fewer than 59 operators in 28 countries have announced plans to deploy LTE on their networks. A sizable number of commercial networks will roll out in 2010. Therefore, vendors of LTE products and infrastructure are performing extensive testing ranging from lab tests on individual devices to small-scale field tests with just a few base stations and user devices from a variety of vendors. Major test networks, too, with numerous base stations and a significant number of initial LTE user devices, are undergoing user trials.

What requirements does this new technology have to meet, and how can you assess and effectively verify LTE performance in a laboratory environment by means of suitable tests? Consider the differences between LTE and other technologies before proceeding to examine the various phases in the development of LTE-enabled infrastructure and end-user equipment.

#### SIMILAR BUT DIFFERENT

The 3GPP participants developed LTE on the basis of available technologies. Therefore, it is hardly surprising that, despite its numerous differences, LTE has a lot in common with them. Consider HSPA(+), an established technology in packet-oriented services. In LTE, just as in HSPA(+), the allocation of resources for the transmission of data from the base station to user equipment relies on a rapid feedback mode in the user device. The device ascertains the quality of the transmission channel and informs the base station what maximum resource size to allocate. The only difference is that LTE offers a much faster feedback mode than does HSPA(+): LTE uses a 1-msec time-transmission interval, whereas HSPA(+) uses a 2-msec TTI and WCDMA uses a 10-msec TTI, allowing the data rate to adapt to current transmission conditions practically every millisecond.

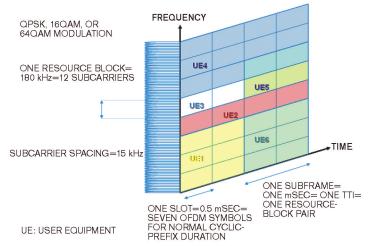

The biggest differences between LTE and current 3GPP standards lie in the technologies manufacturers use to implement the air interface. LTE employs OFDMA and MIMO. In addition, LTE works with a flat IP-based network architecture. OFDMA enables granular resource allocation because LTE uses a large number of narrowband subcarriers with a bandwidth of 15 kHz, compared with 200 kHz in GSM and 5 MHz in WCDMA (Figure 1). This enhancement combines with a maximum channel width of 20 MHz and the ability to work with as many as four transmitting and receiving antennas to create the basic conditions necessary for meeting high-data-rate and high-capacity requirements.

LTE also greatly simplifies the mapping of logical channels onto physical channels. Shared channels have replaced dedicated channels, and LTE has fewer MAC-layer entities and RRC states for greater simplicity. In contrast, the number of parallel processes in the protocol has increased, and you can use MIMO to combine multiple data streams. The encryption function has also changed: In LTE, the eNodeB and MME use different keys. The data in the PDCP layer and the NAS layer are encrypted differently; in WCDMA, the NAS layer is not encrypted at all.

#### **HIGH SPEED, COMPLEXITY**

The way in which LTE integrates into networks also plays a crucial role. From the outset, developers of LTE user equipment have been under enormous time pressure. Even before LTE's core specifications were complete, equipment makers augmented the then-unfinished specifications based on their own assumptions and implemented their own protocol "dialects." Their aim was to be in a position

#### AT A GLANCE

LTE promises end users significant data-rate, network-capacity, and latency improvements.

The biggest differences between LTE and 3GPP standards lie in the technologies to implement the air interface.

LTE will find use in user devices alongside technologies such as WCDMA, CDMA2000, and GSM.

In RF-signaling tests, testers examine the user equipment's transmitter and receiver in combination with all of the signaling layers.

The use of OFDM, which enables TTI-based allocation of resource blocks, leads to significant changes in testing requirements.

NIMO requires extended antenna systems at the base station that you must verify with the aid of signal analyzers.

to demonstrate LTE's ability to function and its benefits as soon as possible. Now that the developers have finalized the specifications to a sufficient degree, the focus is on reducing development time to be able to deliver LTE products to the market as swiftly as possible.

LTE's higher complexity poses signif-

icant challenges because, for the most part, LTE resides in user devices alongside technologies such as WCDMA, CDMA2000, and GSM. The presence of multiple technologies entails a variety of hand-over scenarios, all of which designers must test. In addition, LTE user devices must support other noncellular standards—Wi-Fi, GPS, and Bluetooth, for instance—that complement the wide operational coverage that cellular technologies afford.

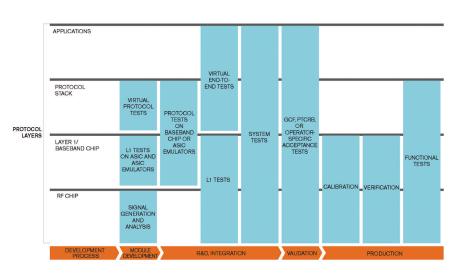

Ideally, to enable steps in the development process for a mobile phone to take place concurrently, developers pursue an approach employing reusable modules. However, the developers must test the various components as early in the process as possible to minimize the number of potential errors during integration and to avoid creating problems in subsequent field tests. The test-and-measurement equipment they use must therefore be able to separately drive or bypass layers or functional modules. The modular approach, for example, enables developers to test the functions they loaded in software onto a baseband chip in a virtual environment without relying on the availability of the hardware.

Other LTE features at the center of development efforts are the data rates on uplinks and downlinks. Just as in

#### LTE GLOSSARY

ACLR: adjacent-channel-leakage ratio AWGN: additive white gaussian noise **BLER:** block-error rate CDMA: code division/multiple access **CPRI:** common public-radio interface **CQI: channel-quality indicator CS: circuit-switched** EDGE: enhanced data rates for GSM evolution eNodeB: base station **ETSI: European Telecommunications Standards** Institute Ev-Do: evolution-data optimized/evolution-data only **EVM:** error-vector magnitude **GCF: Global Certification Forum** GPS: global positioning system GSM: global system for mobile communications HSPA: high-speed packet access I/Q: in-phase/quadrature **IP: Internet Protocol** LTE: long-term evolution **MAC:** medium-access control MIMO: multiple input/multiple output **MME:** mobility-management entity NAS: nonaccess stratum

**OBSAI: Open Base Station Architecture Initiative OFDMA:** orthogonal frequency-division multiple access **PCS:** personal communications service PDCP: Packet Data Convergence Protocol PMI: precoding matrix indicator PRBS: pseudorandom bit sequence **PS:** packet-switched **PTCRB: PCS Type Certification Review Board** QAM: quadrature-amplitude modulation **QPSK:** quadrature phase-shift keying **RI: rank indicator RLC: radio-link control RRC:** radio-resource control **RRH:** remote radio heads 16QAM: 16-phase QAM 64QAM: 64-phase QAM SMS: short-message service **3GPP: Third Generation Partnership Project TTCN2: Testing and Test Control Notation Version 2 TTCN3: Testing and Test Control Notation Version 3** TTI: time-transmission interval **UL CQI: uplink CQI** U plane: user plane WCDMA: wideband CDMA

HSPA(+), they place considerable demands on the user equipment. To assess performance, manufacturers must run tests that evaluate the acknowledgments and negative acknowledgments on the RLC and MAC layers. Designers can achieve the specified data rates using the wide variety of MIMO modes. However, the test-and-measurement equipment must support these modes. Besides the ability to connect multiple antennas, the test equipment must also be able to simulate fading channels. Only then is it possible to test the functioning of receivers under realistic conditions.

Scalable bandwidths and the 17 regional frequency bands further increase the breadth of required testing. And developers must also address limitations, such as different possible power levels in tests at high bandwidths on frequency bands with low separation between receiving and transmitting frequencies.

This high complexity calls for frequent regression tests, such as testing daily software builds or the performance of endurance-testing scenarios in a realistic signal environment. Test equipment with advanced automation and remote capabilities makes it easier to efficiently conduct these tests. The range of measurements is not confined to verifying that developers have correctly implemented the specifications; it also extends to modules' stability and robustness when facing varying interpretations of specifications (**Figure 2**).

At the end of the development process comes conformity testing on certified test systems, during which developers run a selected number of tests from the 3GPP conformance-test specification on the finished user device. Unlike functional tests, this type of testing formally verifies the protocol layers and the requisite RF performance.

#### **MOBILE USER DEVICES**

Testers primarily conduct pure RFperformance testing using signal generators and analyzers; combined RF-signaling tests are also important. These tests examine the user equipment's transmitter-and-receiver combination with all of the signaling layers. The tests are simulations that closely approximate signaling procedures and scenarios in live use under realistic conditions, with possible interfering signals, and during continuous operation of the device. The prima-

Figure 1 LTE employs an OFDMA-modulation scheme that employs a large number of narrowband, 15-kHz subcarriers to enable granular resource allocation.

Figure 2 LTE development involves various module and integration testing procedures as the product moves toward production.

ry emphasis is not on testing the actual signaling procedures; rather, the signaling serves as a means to an end for performing realistic tests on the entire device. Testers perform separate tests for the transmitter and the receiver.

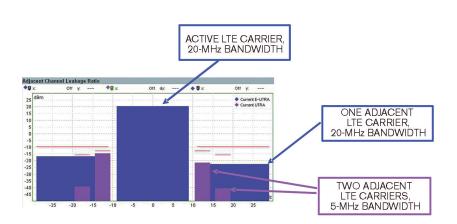

Testers apply a variety of measuring methods during the transmitter tests. First, they test LTE signals using proven methods-power and EVM measurements, for example-they adopted from other mobile-communications technologies. Second, they verify extensive procedures, such as power control based on profiles in LTE and WCDMA. Many of the measurements may resemble wellknown procedures. With LTE, they are more complex, however. A spectrum measurement is a case in point: The fact that LTE and WCDMA frequency bands may be adjacent to each other places exceptional demands on the user equipment. To help prevent interference between neighboring WCDMA and LTE systems, the transmitting power in adjacent bands must not exceed either LTEor WCDMA-specific limits (Figure 3). An extended ACLR test can check that it doesn't.

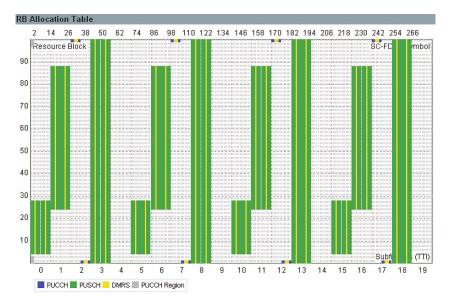

The use of OFDM, which enables TTI-based allocation of resource blocks, has led to significant changes in testing requirements. The measuring equipment must flexibly configure the requisite assignment tables and scheduling parameters for the uplink and downlink and send these tables and parameters to the user equipment. Meanwhile, the testers must check the correct allocation of resource blocks and the transmitting characteristics of the user equipment on the uplink (Figure 4).

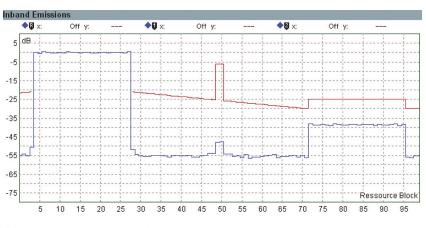

Given that multiple user devices can concurrently use the available bandwidth, testers must measure inband emissions to determine whether the user device complies with allocation and transmitting power requirements on the uplink. This approach ensures that the device does not interfere with other uplink signals outside its allocated resource blocks. Measurement equipment that can flexibly set limits and independently check limits greatly simplifies testing (**Figure 5**).

Because of the breadth of allocation options available, testing generates a large number of results. These results depend extensively on the location

Figure 4 The use of OFDM enables TTI-based allocation of resource blocks; this measurement shows partial allocation of resource blocks.

Figure 5 You must measure inband emissions to determine whether the user device complies with allocation and transmitting power requirements on the uplink.

and size of the allocated resource blocks within the time and frequency domains, and developers must therefore interpret them in context. In addition, some RF impairments have an effect only on certain allocations.

The distribution of transmitting power across multiple subcarriers can lead to power differences between subcarriers. You can examine transmitting power at the subcarrier level by testing spectrum flatness, thereby enabling users to identify potential fluctuations with exceptional precision.

In receiver tests, the MAC layer uses localized acknowledgment/negative-acknowledgment-based BLER methods. These methods for analyzing uplink signals are familiar from HSPA. With LTE MIMO, the focus is on a scenario in which you apply various fading profiles to the downlink signal. To reduce development time and costs, you can use static channel models that simulate a static fading profile instead of dynamic fading profiles. The static models enable you to analyze the effects on receiver behavior using the BLER methods. In HSPA, too, you measure the downlink signal with fading and AWGN. In LTE, other technologies inside and outside the LTE band cause additional interference signals, calling for wider blocking tests and adjacent-channel tests.

The follow-UL-CQI test, again familiar from HSPA, is an important means of adjusting the signaling parameters and thus optimizing the receiving-signal quality that a user device reports through the CQI. Several values affect the quality in LTE, including Rank 1 or Rank 2 CQI, PMI, and RI values. Dynamically changing parameters on active connections in the measuring equipment can help to save time during these tests.

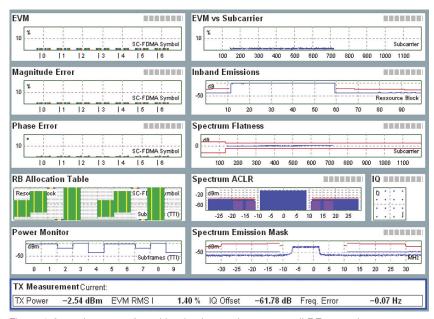

Testing user devices calls for a range of measurement methods suitable for checking the transmitter's RF in combination with the allocated resource blocks on the uplink. Ideally, data for computing transmitter measurements should originate from a test sample and appear simultaneously in a clearly structured form (**Figure 6**).

#### **PERFORMANCE TESTING**

All LTE user devices to date have been data devices-in other words, USB sticks and PC cards. The data-services sector has mainly driven the motivation for introducing LTE. Nevertheless, the continuing debate over technical alternatives for the voice service and the fact that a number of special-interest groups focusing on it have formed within the industry substantiate the emphasis on equally efficient voice support. It remains to be seen which of the alternatives will gain primacy. However, data services pose greater requirements than the voice service as far as protocol test-and-measurement systems are concerned.

In LTE, only the PS domain exists, not the CS domain. In general, multiple services with different bearers operate in parallel in a manner comparable with WCDMA multicall services. Furthermore, once users power up and register their devices, the devices immediately have always-on status and can almost instantly issue requests to transmit data on the uplink or the downlink. Consequently, functional tests spanning all layers always require the measuring equipment to provide a service that delivers data through the U plane.

A mobile device's performance is of direct relevance for end users. How fast is the data rate, and what is the latency when starting services? To what extent does performance degrade when reception is poor? Does the manufac-

Figure 6 A test instrument's multievaluation mode presents all RF-transmitter measurements at a glance.

Figure 7 This constellation diagram for an eNodeB signal shows how multiple elements representing, for example, different data rates or modulation schemes combine into a composite signal.

turer guarantee that the device will interoperate with different base stations? When finding answers to these questions and optimizing a data device, it is not enough simply to check signaling procedures or individual values you measure at the IP level. Rather, it is important to analyze bottlenecks in the protocol layers: Which level is causing unnecessary retransmissions? Why does the BLER increase under certain conditions? Protocol test-and-measurement equipment must answer these questions and verify signaling procedures. Thus, the lines between classic application tests and protocol tests are becoming increasingly blurred.

If you test modules during develop-

ment, the test equipment must provide the necessary interfaces. In the past, it may generally have been sufficient to connect to the user equipment through RF, but it is now essential to provide interfaces on the I/Q baseband because the protocol software runs on the baseband chip or on a chip emulation. It is even possible to completely test a protocol stack without hardware if you replace the physical layer with emulation software. Access to details of lower-level protocol-layer configurations is essential for meeting all these requirements.

Manufacturers will only gradually roll out LTE networks. The rollout will require thorough testing of the handover signaling, as it is important to ensure that user equipment can transition smoothly between technologies. Thus, it is essential for test-and-measurement equipment to provide a basic implementation of all technologies and support for synchronization with LTE. Given that MIMO plays a central role in enabling higher data rates, you must test complex signaling procedures and userdevice feedback.

#### **CONFORMANCE TESTING**

GCF certification of LTE user equipment should begin in late 2010. Validation of the first test cases employing 3GPP specifications 36.521 and 36.523 has occurred. ETSI has chosen TTCN3 as the language for describing the tests. TTCN3 is an enhancement of TTCN2, the language used with WCDMA, and now has more in common with a traditional programming language such as C++. TTCN3 is therefore easier to learn, and adjacent areas of development, in addition to certification tests, will likely adopt it.

In addition to the essential userequipment certification that GCF and PTCRB perform, network operators must also perform certification to their own high standards. These tests place greater emphasis on the characteristics of the network infrastructure and on optimization of the available mobile-communications services.

#### **A CHANGE OF PERSPECTIVE**

The swift and efficient development of LTE base stations represents a core challenge for infrastructure vendors. As a rule, they deploy test systems well be-

#### TABLE 1 MEASUREMENTS ON TRANSMITTERS AND RECEIVERS

| Transmitter                                      | Receiver                                                                                     |  |

|--------------------------------------------------|----------------------------------------------------------------------------------------------|--|

| Output power and dynamic range of output power   | Sensitivity and receiver dynamic range                                                       |  |

| Signal quality, such as frequency errors and EVM | Channel selectivity                                                                          |  |

| Unwanted emissions                               | Immunity to interference with adjacent inter-<br>fering signals on frequency band (blocking) |  |

| Transmitter intermodulation                      | Interfering emissions in the receiver                                                        |  |

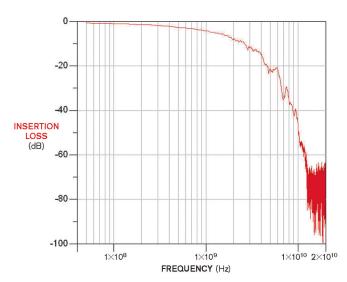

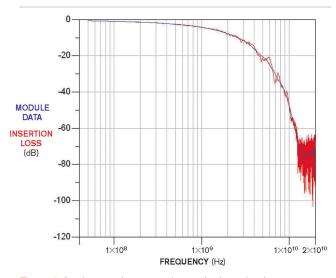

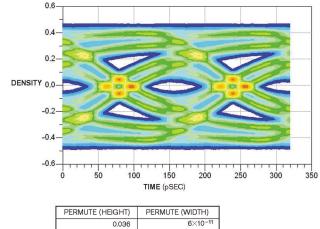

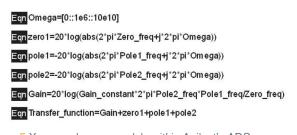

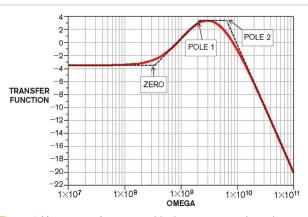

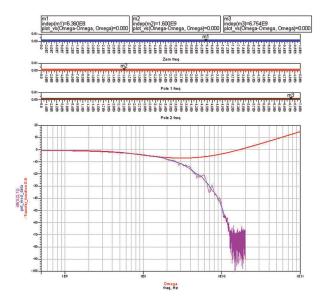

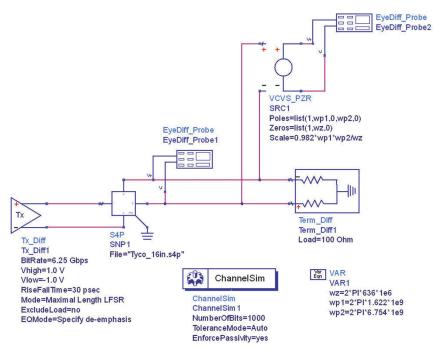

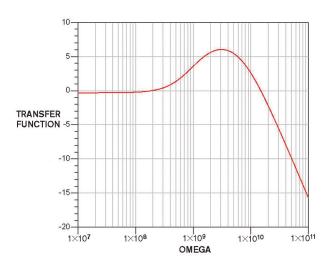

|                                                  | Receiver intermodulation                                                                     |  |